March 2016 VOLUME -1 ISSUE-3 Page:7796-03

# Partial Feedback Linearizing Voltage Stabilization By A Multi Level Dc–Ac Converter With A Novel PWM

Yeddu Kiran\*<sup>1</sup>: Gayatri.Buddharaju<sup>2</sup>: K.Venkata Ratnam<sup>3</sup>

<sup>1</sup> M.tech (PE) Student Department Of EEE, Sri Sivani Institute Of Technology Chilakapalem.

<sup>2</sup> Head Of The Department Of EEE, Sri Sivani Institute Of Technology Chilakapalem.

<sup>3</sup> Assistant Professor Of EEE, Sri Sivani Institute Of Technology Chilakapalem.

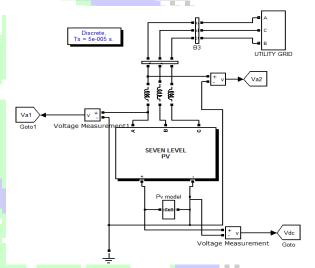

**ABSTRACT:** This paper proposes a system of converters for the integration of a large photovoltaic (PV) plant with a utility AC grid. The system comprises of a central seven-level voltage-fed inverter (VFI) and a large number of PV modules with moduleintegrated DC-DC converter. The sevenlevel VFI consists of three three-phase, three-level VFI units connected in parallel on the AC-side. This paper also proposes a new solar power generation system, which is composed of a DC/DC & DC/AC power converter and a new seven-level inverter. This new seven-level inverter is configured using a capacitor selection circuit and a fullbridge power converter, connected in cascade. Seven level converts fed with PV

modules provide a viable solution to mitigating harmonic related issues caused by diode or thyristor rectifier front-ends. To handle the large compensation currents and provide better thermal management, two or more paralleled semiconductor switching devices can be used. The proposed PV based seven level topology can also produce seven voltage levels, which significantly reduces the switching current ripple and the size of passive components. The performance of the proposed power converters system is studied using MATLAB/Simulink.

**I.INTRODUCTION:** With the rapid consumption of fossil energy resources and the deterioration of ecological environment,

### International Journal of Engineering In Advanced Research Science and Technology ISSN: 2278-256

March 2016 VOLUME -2 ISSUE-3 Page:7796-03

especially the global climate change caused by greenhouse gas emissions, sustainable development of human society is confronted with serious threats. The development and the use of renewable energy have drawn extensive attention of the international society. Many countries have made definite development goals, and carried out policies and regulations for renewable energy. These policies and regulations guarantee the boost of renewable energy technology and realize the diversification of energy. Solar energy, as a type of renewable energy, is widely applied in manufacturing and living activities. The use of it mainly includes: solar photovoltaic, solar thermal power generation, solar water heater and solar house, etc. The application of solar water heater is already well integrated with architecture in developed countries, and is developing towards the direction of solar architecture integration. In recent years, multilevel converters have shown some significant advantages over traditional twolevel converters, especially for high-power and high-voltage applications. In addition to their superior output voltage quality, they can also reduce voltage stress across

switching devices. Since the output voltages have multiple levels, lower dv/dt is achieved. which greatly alleviates electromagnetic interference problems due high-frequency switching Multilevel inverters (MLI) started with the neutral point clamped inverter topology proposed by Nabae et al. Presently multilevel inverters have become more attractive for researchers due to their advantages over conventional three-level Pulse width-modulated (PWM) inverters. MLI has two main advantages compared with the conventional H-bridge inverters, the higher voltage capability and the reduced harmonic content in the output waveform due to the multiple de levels. MLI is now preferred in high power medium voltage applications due to the reduced voltage stresses on the devices. MLI incorporates a topological structure that allows a desired output voltage to be synthesized among a set of isolated or interconnected distinct the voltage sources. Numerous topologies realize this connectivity and can be generally divided into three major categories namely, diode clamped MLI, flying capacitor MLI and separated dc sources

(cascaded voltages) MLI. Recently nonconventional energy sources for grid connected applications are increased due to the world energy crisis. Injecting power to the utility must meet the world harmonic standards. Therefore, single phase MLIs become a good solution for most particular demerits of MLI is the large number of the required power semiconductor switches. Although low voltage rate switches can be utilized in a multilevel inverter, each switch requires a related gate drive circuit. This may be problem occurs, the overall system to be

more expensive and complex. So, in practical implementation, decreasing the number of switches and gate driver circuits have become an essential point. Recently, so many topologies of the MLI and its control techniques have been published. The MLI technique is implemented in by adding one switch and four power diodes to the

# II. ORIGIN OF LOWER ORDER HARMONICS AND FUNDAMENTAL CURRENT CONTROL

This section discusses the origin of the lower order harmonics in the system under

consideration. The sources of these harmonics are not modeled as the method proposed to attenuate them works independent of the harmonic source. The fundamental current control using the proposed multi level converter pi based controller is also explained.

#### A. Origin of Lower Order Harmonics

1) Odd Harmonics: The dominant causes for the lower order odd harmonics are the distorted magnetizing current drawn by the transformer, the inverter dead time, and the semiconductor device voltage drops. Other factors are the distortion in the grid voltage itself and the voltage ripple in the dc bus. The magnetizing current drawn by the transformer contains lower order harmonics due to the nonlinear characteristics of the B-H curve of the core. The exact amplitude of the harmonics drawn can be obtained theoretically if the B-H curve of the transformer is known. The phase angle of the harmonics due to the magnetizing current will depend on the power factor

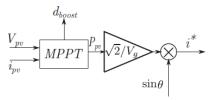

Fig.1. Generation of an inverter ac current reference from an MPPT block.

of operation of the system. As the operation will be at unity power factor (UPF), the current injected to the grid will be in phase with the grid voltage. However, the magnetizing current lags the grid voltage by 90°. Hence, the harmonic currents will have a phase displacement of either  $+90^{\circ}$  or  $-90^{\circ}$ depending on harmonic order. The deadeffect introduces lower time order harmonics which are proportional to the dead time, switching frequency, and the dc bus voltage. The dead-time effect for each leg of the inverter can be modeled as a square wave error voltage out of phase with the current at the pole of the leg. The device drops also will cause a similar effect but the resulting amount of distortion is smaller compared to that due to the dead time. Thus, single-phase inverter for topology considered, net error voltage is the voltage between the poles and is out of phase with the primary current of the transformer. The harmonic voltage

amplitude for a *h*th harmonic can be expressed as

Verror =  $4h\pi 2V dct dTs$  (1)

where td is the dead time, Ts is the device switching frequency, and Vdc is the dc bus voltage. Using the values of the filter inductance, transformer leakage inductance, and the net series resistance, the harmonic current magnitudes can be evaluated. Again, it must be noted that the phase angle of the harmonic currents in this case will be 180° for UPF operation. Thus, it can be observed that the net harmonic content will have some phase angle with respect to the fundamental the relative current depending on magnitudes of the distortions due to the magnetizing current and the dead time.

## III. SEVEN LEVEL PV CONVERTER TOPOLOGY

The proposed seven level topology is shown in Fig. It consists of an H-bridge configuration made from three-level flying capacitor branches. Essentially, it is a voltage-source inverter (VSI) with capacitive energy storage (Cdc) shared by all three phases. Total of eight switching devices are used in each phase. A tapped reactor is used to connect the two legs of the Hbridge. Typically, the reactor is wound to

be center tapped, making the output line-toground voltages (vag for example) the average of the voltages from each side of the H-bridge. Then, the line-to-ground voltages will have five distinct voltage levels. However, with this topology, the tap is set at 1/3. This results in seven distinct output voltages, and therefore, improves the power quality. The switching operation is described next, wherein all seven levels are clearly illustrated.

Fig2. Proposed seven-level PV converter topology

TABLE I Seven Level Converter Line-To-Ground Voltages

| $S_a$ | $v_{a1}$       | $v_{a2}$       | $v_{ag}$            |

|-------|----------------|----------------|---------------------|

| О     | О              | О              | О                   |

| 1     | О              | $v_{\rm dc}/2$ | $v_{\rm dc}/6$      |

| 2     | $v_{\rm dc}/2$ | О              | $v_{\rm dc}/3$      |

| 2'    | О              | $v_{ m dc}$    | $v_{\rm dc}/3$      |

| 3     | $v_{\rm dc}/2$ | $v_{\rm dc}/2$ | $v_{\rm dc}/2$      |

| 4     | $v_{\rm dc}/2$ | $v_{ m dc}$    | $2v_{\rm dc}/3$     |

| 4'    | $v_{ m dc}$    | О              | $2v_{\rm dc}/3$     |

| 5     | $v_{ m dc}$    | $v_{\rm dc}/2$ | 5v <sub>dc</sub> /6 |

| 6     | $v_{ m dc}$    | $v_{ m dc}$    | $v_{ m dc}$         |

- 1) The core of the reactor is highly permeable in a sense that it requires vanishingly small magneto motive force to set up the flux.

- 2) The core does not exhibit any eddy current or hysteresis loss.

- 3) All the flux is confined in the core, so there is no leakage flux.

- 4) The resistance of the reactor is negligible. Suppose that voltages vx1 and vx2, with respect to a common ground, are applied to the input terminals x1 and x2, respectively. For this ideal model, it is straightforward to determine the voltage between the output terminal x and terminal x2

$$v_{xx2} = \left(\frac{N_2}{N_1 + N_2}\right) (v_{x1} - v_{x2}) = \frac{2}{3} (v_{x1} - v_{x2}).$$

The voltage at the output terminal with respect to the common ground is therefore

$$v_{xg} = v_{xx2} + v_{x2} = \frac{2}{3}v_{x1} + \frac{1}{3}v_{x2}.$$

In the general analysis presented earlier, x represents a phase, and the phase may be a, b, or c. Each leg of the H-bridge has a voltage-clamping capacitor, and the voltages at the two input terminals of the reactor can be 0, vdc/2, or vdc, where vdc is the nominal voltage of the capacitor Cdc, as shown in Fig.

For each phase, there are nine different switching states, corresponding to nine terminal voltage combinations. These combinations can produce a line-to-ground voltage at the output terminal that has seven distinct voltage levels. For phase a, these states are detailed in Table I.

In Table I, sa is the switching state that is defined as being 0 for the lowest possible line-to-ground voltage. The voltage vag is as defined in Fig. And calculated using . Note that there are two redundant states 2\_ and 4\_ that produce the same voltage as states 2 and 4, respectively.

However, these are not desirable, and will be ignored, because the voltages applied across the reactor are twice as high as the other states. The output current for each phase is split between the two legs of the H-bridge structure. Ideally, two-thirds of the current will come from x1 and one-third from x2 so that the magnetizing current is zero. The control given later discusses the regulation of the reactor currents so as to minimize the magnetizing current.

#### **Multilevel Voltage-Source Modulation**

The seven-level voltage-source modulation is accomplished by comparing the duty cycles with a set of six carrier waveforms. This is illustrated for phase a in Fig. The resulting switching state sa is the number of triangle waveforms that the duty cycle is greater than. Therefore, the switching state has a range of 0–6, and this is in agreement with Table I.

#### **Capacitor Voltage Balancing**

After carrying out the modulation, the switching states for each phase need to be broken out into transistor signals. In order to have the correct voltage levels, the flying capacitors must remain charged at exactly vdc/2. This can easily be assured using the redundancy of the inverter legs.

TABLE II

| $S_{1a}$ | $s_{2a}$ | $v_{a1}$   | $i_{af1}$ | Charging |

|----------|----------|------------|-----------|----------|

| 0        | 0        | 0          | +         | 0        |

| 0        | 0        | 0          | _         | 0        |

| 1        | 1        | $v_{dc}$   | +         | 0        |

| 1        | 1        | $v_{dc}$   | +         | 0        |

| 0        | 1        | $v_{dc}/2$ | +         | _        |

| 0        | 1        | $v_{dc}/2$ | _         | +        |

| 1        | 0        | $v_{dc}/2$ | +         | +        |

| 1        | 0        | $v_{dc}/2$ | _         | _        |

# SIMULATION RESULTS & DISCUSSIONS

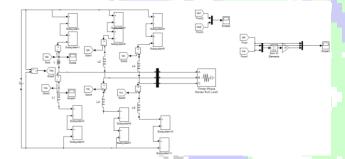

Fig3. propsed Circuit

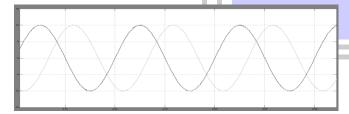

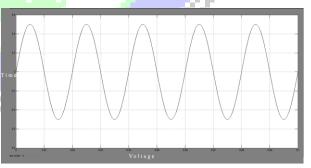

FIG.4 unbalanced voltages with proposed converter

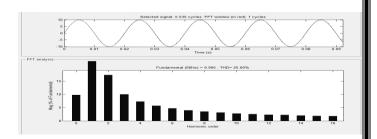

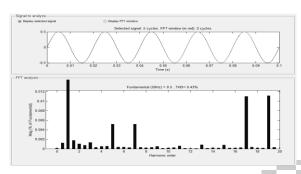

Fig 5. THD analysis of unbalanced voltages with proposed converter

Fig.9 extension seven level Circuit

FIG.10 balanced voltages with Seven level converter

Fig.11 THD analysis of balanced voltages with seven level converter

Fig. 12 seven level voltages of proposed converter

#### CONCLUSION

This paper has presented "A New topology of Single-Phase Seven-Level Inverter with Less Number of Power Elements for Grid Connection". The control technique is pulse generation for switches in the proposed inverter. All switches in proposed inverter operated with fundamental frequency. So, switching losses and THD value are low in the proposed inverter. The future scope is photovoltaic arrays, fuel cells used in this proposed inverter. The details of the high-level control as well as the switching control have been presented. The proposed seven

level has been validated for a power grid power system using detailed simulation.

#### **REFERENCES**

- Kulkarni And John: Mitigation Of Lower

Order Harmonics In A Grid-Connected

Single-Phase Pv Inverter

- 2. C. W. Chou is with the Department of Microelectronic Engineering, National Kaohsiung Marine University, Kaohsiung, Taiwan, R.O.C.

- [3] M. Hanif, M. Basu, K. Gaughan., "Understanding the operation of a Z-source inverter for photovoltaic application with a design example," *IET Power Electron.*, Vol. 4, No. 3, pp.278-287, 2011.

- [4] J, M. Shen, H. L. Jou, J. C. Wu, "Novel Transformer-less Grid-connected Power Converter with Negative Grounding for Photovoltaic Generation System," *IEEE Trans. Power Electronics*, Vol. 27, No. 4, pp.1818-1829, 2012.

- [5] N. Mohan, T. M. Undeland, W. P. Robbins, *Power Electronics Converters, Applications and Design*, Media Enhanced 3rd ed. New York: John Wiely& Sons, 2003.

- [6] K. Hasegawa, H. Akagi, "Low-Modulation-Index Operation of a Five-Level Diode-Clamped PWM Inverter With a DC-Voltage-Balancing Circuit for a Motor Drive," *IEEE Trans. Power Electron.*, Vol. 27, No. 8, pp.3495-3505, 2012.

- [7] J. Huang and K. A. Corzine, "Extended operation of flying capacitor multilevel inverters," IEEE Trans. Power Electron., vol. 21, no. 1, pp. 140–147, Jan. 2006.

- [8] P. Xiao, K. A. Corzine, and G. K. Venayagamoorthy, "A novel sevenlevel shunt active filter for high-power drive systems," in Proc. IEEE Ind. Electron. Soc. Conf., Paris, France, Nov. 2006, pp. 2262–2267.

- [9] F. Ueda, K. Matsui, M. Asao, and K. Tsuboi, "Parallel-connections of pulse width modulated inverters using current sharing reactors," IEEE Trans. Power Electron., vol. 10, no. 6, pp. 673–679, Nov. 1995.

- [10] H. Mori, K.Matsui, K. Kondo, I. Yamamoto, and M. Hasegawa, "Parallel connected five-level PWM inverters," IEEE Trans. Power Electron., vol. 18, no. 1, pp. 173–179, Jan. 2003.