April 2016 VOLUME -1 ISSUE-4

Page:7905-06

# A DISTINET DESIGN OF OPERATIONAL AMPLIFIER OF LOW VOLTAGE LOW POWER

<sup>1</sup>.Durga prasad bolla, <sup>2</sup>. V.KRISHNAN, <sup>3</sup>. S.n.v.p raviteja

- <sup>1</sup>.PG Scholar, <u>durgaprashadbolla@gmail.com</u>, Dept of ECE, Sasi institute of technology and engineering.

- <sup>2</sup>. Assistant professor, <u>krishnan@sasi.ac.in</u>, Dept of ECE, Sasi institute of technology and engineering <sup>3</sup>. Assistant professor, <u>raviteja@sasi.ac.in</u>, Dept of ECE, Sasi institute of technology and engineering

**ABSTRACT:** This Thesis presents a design of the Folded-cascade operational amplifier which leads to high gain as compared to a normal cascade circuit. In this project; specifications of analog systems into op amp level net-lists of library components is studied and simulated using XILINX. As the power-supply voltages because of the technology improvement and it are desired to power supply to minimize power dissipation, many challenges face the analog designer. One is to keep noise level as possible. The op-amp must be designed to with the ever decreasing power supply voltages. As the power supply voltages begin to approach 2Vt, new technique and new op-amp topology like folded cascade should be used.

**KEYWORDS:** complementary metal-oxide semiconductor, common-mode range, Power-supply rejection ratio, CASCODE, Slew Rate

#### INTRODUCTION:

The design of op amps continues to pose a challenge as the supply voltage and transistor channel length scale down with each generation of CMOS technologies. Operational amplifiers are the amplifier (controlled sources) that has sufficiently high gain so that when negative feedback is applied, the closed loop transfer function is practically independent of the gain of the op amp. This principle has been exploited to develop many useful analog circuits and systems. The primary requirement of an op amp is to have an open-loop gain that is sufficiently large to implement the negative feedback concept. Controlled linear sources and passive linear devices such as generic models for resistors, capacitors and inductors were presented [1-3]. This communication shows this method is applicable to some active devices like high loop gain operational amplifiers (Op-Amps). A generic amplifier model is presented allowing for user defined feedback networks. As the channel lengths of CMOS technology decrease, the maximum allowable voltage will decrease. Also, as more components are included in the same area on

integrated circuits, the power dissipation increases. Finally, the requirement for portable electronics implies battery operation which favors low voltage and low power circuits. These factors and others have caused many to suggest that future implementation of mixed analog digital circuits using standard CMOS will have power supplies of 1.5V or less an important factor concerning analog circuits is that the threshold voltages of future standard CMOS technologies are not anticipated to decrease much below what is available today[1,2]. It is necessary that the analog power supply be at least equal to the sum of the magnitudes of the nchannel and p-channel thresholds. This implies that low voltage analog circuits are incompatible with the CMOS technology trends of the future. Ways to circumvent this conflict are to develop technologies with lower thresholds, increase the lower voltage power supply by on-chip dc-dc converter, or develop circuit techniques that are compatible with future standard CMOS technology trends.

This paper will briefly review some of the limitations of analog circuits at low voltage. Next, circuit methods of using existing CMOS technology will be described that permit analog circuit operation at low voltages. Each of these methods alone cannot solve the problem but together they offer attractive solutions. One of these methods which are unique with this paper is the channel JFET and its operation and characterization are presented in detail. Next, it is shown how to use these methods to implement analog circuit building blocks such as current sinks/sources, differential amplifiers, and current mirrors.

**OP-AMP:** An **operational amplifier** (op-amp) is a DC-coupled high-gain electronic voltage amplifier with a differential input and, usually, a single-ended output. An op-amp produces an output voltage that is typically hundreds of thousands of times larger than the voltage *difference* between its input terminals.

Page:7905-06

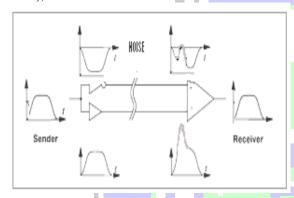

**Differential signaling** is a method of transmitting information electrically with two complementary signals sent on two paired wires, called a differential pair. Since external interference tend to affect both wires together, and information is sent only by the difference between the wires, the technique improves resistance to electromagnetic noise compared with use of only one wire and an un-paired reference (ground). The technique can be used for both analog signaling, as in balanced audio, and digital signaling, as in RS-422, RS-485, Ethernet over twisted pair, PCI Express, DisplayPort, HDMI, and USB. The opposite technique is called single-ended signaling. Differential pairs are usually found on a printed circuit board, in cables (twisted-pair cables, ribbon cables), and in connectors

# **Tolerance of ground offsets**

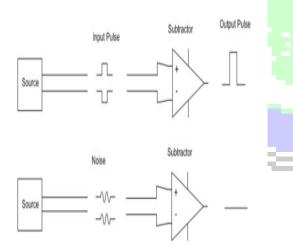

In a system with a differential receiver, desired signals add and noise is subtracted away.

At the end of the connection, the receiving device reads the difference between the two signals. Since the receiver ignores the wires' voltages with respect to ground, small changes in ground potential between transmitter and receiver do not affect the receiver's ability to detect the signal.

Operational amplifiers had their origins in analog computers, where they were used to do mathematical operations in many linear, non-linear and frequency-dependent circuits. Characteristics of a circuit using an op-amp are set by external components with little dependence on temperature changes or manufacturing variations in the op-amp itself, which makes op-amps popular building blocks for circuit design.

Op-amps are among the most widely used electronic devices today, being used in a vast array of consumer, industrial, and scientific devices. Many standard IC op-amps cost only a few cents in moderate production volume; however some integrated or hybrid operational amplifiers with special performance specifications may cost over \$100 US in small quantities Op-amps may be packaged as components, or used as elements of more complex integrated circuits.

The op-amp is one type of differential amplifier. Other types of differential amplifier include the fully differential amplifier (similar to the op-amp, but with two outputs), the instrumentation amplifier (usually built from three op-amps), the isolation amplifier (similar to the instrumentation amplifier, but with tolerance to common-mode voltages that would destroy an ordinary op-amp), and negative feedback amplifier (usually built from one or more op-amps and a resistive feedback network).

## **Input Common Mode Voltage Range**

The Input Common Mode Voltage is defined as the average voltage at the inverting and non-inverting input pins.

1. If the common mode voltage gets too high or too low, the inputs will shut down and proper operation ceases. The common mode input voltage range, CMVR, specifies the range over which normal operation is guaranteed.

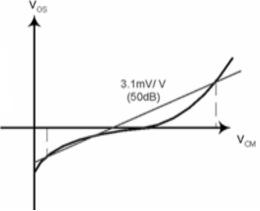

This graph shows Input Offset Voltage vs. Common Mode Voltage. The blue line is the actual

April 2016 VOLUME -2 ISSUE-4 Page:7905-06

measured value of the input common mode voltage. The red line is the calculated value.

- 1. The upper limit is determined by the saturation point of one of the two input transistors.

- 2. The lower limit is determined by the transistor which supplies the bias current.

# Advantages of cascaded op-amp:

voltage level and is defined as the average voltage

at the inverting and non-inverting input pins.

- a) Good common-mode range

- b) Self compensation

- c) High gain

- d) Relatively low power-dissipation

- e) High output resistance

## Defining input common-mode range

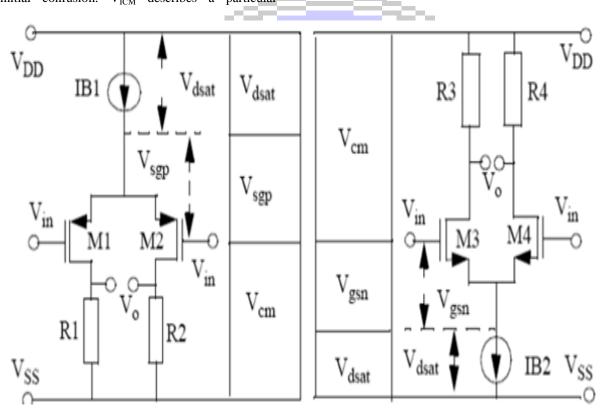

When speaking of op amp inputs, input common-mode voltage  $(V_{ICM})$  is one of the first terms of which an engineer thinks, but may lead to some initial confusion.  $V_{ICM}$  describes a particular

Fig1: The common-mode input range of a p-channel and an n-channel differential pair

For a p-channel pair, the common mode input voltage range is given by:

$VSS \le Vcommon \le VDD - Vdsat - Vsgp$

Where Vcommon is the common mode input voltage, Vsgp is the source-gate voltage of an input transistor, Vdsat is the voltage across a current

source, VDD is the positive supply voltage, and VSS is the negative supply voltage.

For an n-channel input pair, the common mode input voltage is given by:

$VSS + Vgsn + Vdsat \le Vcommon \le VDD$ .

Where Vgsn is the gate source voltage of an nchannel input transistor.

April 2016 VOLUME -2 ISSUE-4 Page:7905-06

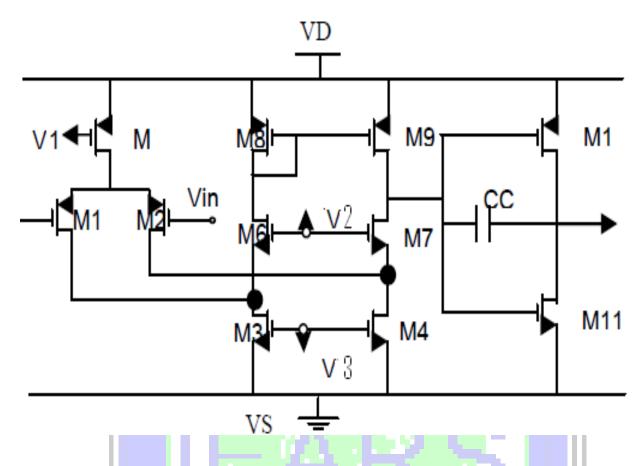

Fig2. Case coded Low voltage, Low power OP-AMP

This architecture does not required perfect balance of current in differential amplifier because excess dc currentcan flow into or out of the current mirror, because the drains of M1 and M2 are connected to drains of M4 an M5. The bias current I(M5), I(M3) and I(M4) are designed so that the dc current through current mirror never be zero. If this current goes to zero then, this requires a delay in turning the mirror back on because of the parasitic capacitances that must be charged. For example if Vid the differential voltage is large enough to turn M1 on and M2 off. Then all of the I(M5) flows through the M1 and none through M2, resulting in I(M5)=I(M1) and I(M2)=0. If I(M3) and I(M4) are not greater than I(M5) then the current through M8 will be zero. To avoid this we have to take I(M3) and I(M4) normally between I(M5) and 2I(M5). In the current design this is I(M3)=I(M4)=1.5 times the I(M5).

#### **Simulation Result:**

| Simulation Simulation                 |        |            |                      |  |

|---------------------------------------|--------|------------|----------------------|--|

| File View Test Bench Smylation Window |        |            |                      |  |

| † 本作性 P P X X ( 図   (を ) / 2   1000   |        |            |                      |  |

| Now:<br>10000 ns                      |        | ns 2000    | 4000 ns 6000 6000 ns |  |

| ⊞ (x1_re(31:0)                        | 66 (   |            | 66                   |  |

| ⊞ <mark>(</mark> x1_im(31:0)          | 64 (   |            | 64                   |  |

| ⊞ 🐧 x2_re[31:0]                       | 6 (    |            | 6                    |  |

| ⊞ <mark>(</mark> x2_im(31:0)          | 6 (    |            | 6                    |  |

| ⊞ (X3_re[31:0]                        | 6 (    |            | 6                    |  |

| ⊞ <mark>(</mark> x3_im(31:0)          | 6 (    |            | 6                    |  |

| ⊞ (X x4_re[31:0]                      | 6 (    |            | 6                    |  |

| ⊞ (31:0) ± 34_im                      | 6 (    |            | 6                    |  |

| ⊞ (w1_re[31:0]                        | 16384( |            | 16384                |  |

| ⊞ (31:0)                              | 8 (    |            | 8                    |  |

|                                       | 65536( |            | 65536                |  |

| ⊞ (31:0) w2_im(31:0)                  | 32 (   |            | 32                   |  |

|                                       | 64 (   |            | 64                   |  |

| ⊞ (31:0) w3_im(31:0)                  | 512 (  |            | 512                  |  |

| ⊞ (31:0] ⊞ (31:0]                     | 429 (  | 4294966848 |                      |  |

| ⊞ <b>[</b> 31:0]                      | 110_ ( |            | 1107378792           |  |

| ⊕ <b>(</b> y2_re(31:0)                | 427(   | 4278189956 |                      |  |

| ⊞ <b>3</b> y2_im[31:0]                | 108 (  | 1086373336 |                      |  |

| ⊞ 🐧 y3_re[31:0]                       | 427(   | 4278189956 |                      |  |

| ⊞ <b>3</b> y3_im[31:0]                | 109 (  | 1090567640 |                      |  |

| ⊞ <b>3</b> y4_re[31:0]                | 426 (  |            | 4261412752           |  |

April 2016 VOLUME -2 ISSUE-4

Page:7905-06

# Synthesis Results: EXISTING TECHNIQUE:

PROPOSED TECHNIQUE

#### CONCLUSION:

This Thesis presents a complete behavioral, simulation and synthesis method in analog systems for cascaded op amp. Folded cascade op-amp is a better solution for low voltage low power operation as compared to conventional op-amp. It provides

large ICMR and better frequency performance, which is required for low voltage operation and can be designed for low power operation also. Finally, by applying clock gating technique to cascaded opamp; total dissipated power is reduced and enhanced op-amp is yielded.

#### REFERENCES:

- [1] Allen/Holberg CMOS Analog Circuit Design (Second ed. 2002) Oxford University Press

- [2] Prof. Andreas König Electronics II Script WS 07/08

- [3] Prof. Andreas König TESYS Script SS 08

- [4] Martin Hetterich Untersuchung der Realisierbarkeit eines generisch rekonfigurierbaren Sensorelektronikbausteins in einer 0,35μm Hochvolt-CMOS-Technologie 2009 *CMOSInstrumentation Amplifier*" IEEE JSSC, vol, Sc-12, pp 805-807, June 1985

- [6] Haluk Kulah and Tayfun Akin "A Current Mirroring Integration Based Readout circuits for high performance infrared circuits for high Performance infrared FPA application". IEEE transactions on circuits And systems-II Analog and digital signal processing, vol-50.

- [7] Antonio J lopez-Martin, Sushmita Baswa, Jaime Ramirez-Angula and Ramon Gonzalez Carvajal"Low Voltage Super Class AB CMOS OTA Cells with very high slew rate and Power efficiency".IEEE JSSC, vol- 40, No-5, pp-1068-1077, May2005.

- [8] R.Harjani, R.Heinekeand F.Wang. "An Integrated Low-Voltage Class AB CMOS OTA" IEEE JSSC, vol-34, no-2, p.p. 134-142, Feb-1999. [9] S.Baswa, A.J Lopez-martin, J.Ramirez-Angula, and R.G.Carvajal "Low Voltage Micropower Super Class AB CMOS OTA" Electronic Lett. Vol-34, no-2, p.p134-142, Feb-1999.