December 2016 VOLUME -2 ISSUE-4

Page: 7917-22

# A NEW THREE PHASE MULTILEVEL INVERTER WITH REDUCED NUMBER OF POWER ELECTRONIC COMPONENTS

#### 1. JYOTHI N,2. M.PRATHIBHA

PG Scholar, Dept o EEE, Kodada Institute of Technology & Science for Women, Kodada.

Guide, Dept of EEE, Kodada Institute of Technology & Science for Women, Kodada

ABSTRACT- In this paper, a new configuration of a three-phase nine-level multilevel voltage-source inverter is introduced along with fuzzy logic. A multilevel dc link using fixed dc voltage supply and cascaded half-bridge is connected in such a way that the proposed inverter outputs the required output voltage levels. Here we are using fuzzy logic controller instead of using other controllers. The fundamental frequency staircase modulation technique is easily used to generate the appropriate switching gate signals. For the purpose of increasing the number of voltage levels with fewer number of power electronic components, the structure of the proposed inverter is extended and different methods to determine the magnitudes of utilized dc voltage supplies are suggested. Moreover, the prototype of the suggested configuration is manufactured as the obtained simulation and hardware results ensured the feasibility of the configuration and the compatibility of the modulation technique is accurately noted.

Index terms – Bidirectional switch, fundamental frequency staircase modulation, multilevel inverter, Fuzzy logic.

#### I. INTRODUCTION

On the other hand, for the purpose of improving the performance of the conventional singleand three-phase inverters, different topologies employing different types of bidirectional switches have been suggested. Comparing to the unidirectional one, bidirectional switch is able to conduct the current and withstanding the voltage in both directions. Bidirectional switches with an appropriate control technique can improve the performance of multilevel inverters in terms of reducing the number of semiconductor components, minimizing withstanding voltage and achieving the desired output voltage with higher levels. Based on this technical background, this paper suggests a novel topology for a three phase nine-level multilevel inverter.

Multilevel inverters consist of a group of switching devices and dc voltage supplies, the output of which produces voltages with stepped waveforms. Multilevel technology has started with the three-level converter followed by numerous multilevel converter topologies. Different topologies and wide variety of control methods have been developed in the recent

literature. The most common multilevel inverter configurations are neutral point clamped (NPC), the flying capacitor (FC), and the cascaded H-bridge (CHB). The deviating voltage of neutral-point voltage NPC, the unbalanced voltage dc link of FC, and the large number of separated dc supplies in CHB are considered the main drawbacks of these topologies. Apart from these three main topologies, other topologies are introduced. Recently, asymmetrical and hybrid multistage topologies are becoming one of the most interested research area. In the asymmetrical configurations, the magnitudes of dc voltage supplies are unequal. These topologies reduce the cost and size of the inverter and improve the reliability since minimum number of power electronic components, capacitors, and dc supplies are used. The hybrid multistage converters consist of different multilevel configurations with unequal dc voltage supplies. With such converters, different modulation and power strategies electronic components technologies are needed.

The number of switching devices, insulated-gate driver circuits, and installation area and cost are significantly reduced. The magnitudes of the utilized dc voltage supplies have been selected in a way that brings the high number of voltage level with an effective application of a fundamental frequency staircase modulation technique. Extended structure for *N*-level is also presented and compared with the conventional well-known multilevel inverters. Simulation and hardware results are given and explained.

#### II. PROPOSED TOPOLOGY

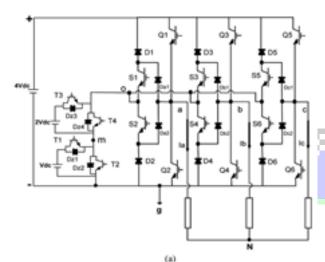

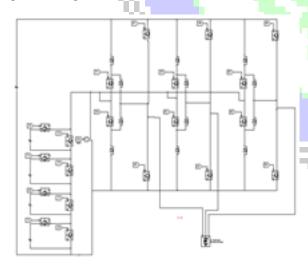

Fig.1shows the typical configuration of the proposed three-phase nine-level multilevel inverter. Three bidirectional switches (S1–S6, Da1–Dc2), two switches—two diodes type, are added to the conventional three-phase two-level bridge (Q1–Q6). The function of these bidirectional switches is to block the higher voltage and ease current flow to and from the midpoint (o). A multilevel dc link built by a single dc voltage supply with fixed magnitude of 4Vdc and CHB having four dc

voltage supplies of Vdc, Vdc and 2Vdc, 2Vdcare connected to (+, -, o)bridge terminals.

Fig. 1. Circuit diagram of the proposed three-phase 9-level multilevel inverter

Based on the desired number of output voltage levels, a number of CHB cells are used. Since the proposed inverter is designed to achieve nine voltage levels, the power circuit of the CHB makes use of four series cells having two unequal dc voltage supplies. In each cell, the two switches are turned ON and OFF under inverted conditions to output different voltage levels.

The first cell dc voltage supply Vdc is added if switch T1 is turned ON leading to Vmg = +Vdc where Vmg is the voltage at node (m) with respect to inverter ground(g) or bypassed if switch T2 is turned ON leading to Vmg=0. Likewise, the second cell dc voltage supply 2Vdc is added when switch T3 is turned ON resulting in Vom=+2Vdc where Vom is the voltage at midpoint (o) with respect to node (m) or bypassed when switch T4 is turned ON resulting in Vom= 0. The peak voltage rating of the switches of the conventional two level bridge (Q1– Q6) is 4Vdc whereas the bidirectional switches(S1–S6) have a peak voltage rating of 3Vdc. In CHB cells, the peak voltage rating of second cell switches (T3 and T4) is 2Vdcwhile the peak voltage rating of T1 and T2 in the first cell is Vdc .By considering phase a, the operating status of the switches and the inverter line-to-ground voltage Vag are given in Table I.

# TABLE I:

Switching State Sa and Inverter Line-to-Ground Voltage

It is easier to define the inverter line-to-ground voltages Vag, Vbg, and Vcg in terms of switching states Sa, Sb, and Scas

$$=-$$

\*  $(1)$

Where N = 5 is the maximum number of voltage levels. The balanced load voltages can be achieved if the proposed inverter operates on the switching states depicted in Table II. The inverter may have 24 different modes within a cycle of the output waveform. According to Table II, it can be noticed that the bidirectional switches operate in 18 modes. For each mode, there is no more than one bidirectional switch in on state.

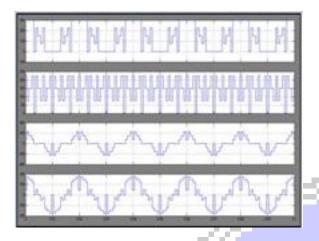

As a result, the load current commutates over one switch and one diode (for instance; in (410), the load current *I*b can flow in S3 and Db1 or S4 and Db2). Since some insulated ate bipolar transistors (IGBTs) share the same switching gate signals, the proposed configuration significantly contributed in reducing the utilized gate driver circuits and system complexity. The inverter line-to-line voltage waveforms *V*ab, *V*bc, and *V*ca with corresponding switching gate signals are depicted in Fig. 2where *V*ab, *V*bc, and *V*ca are related to *V*ag, *V*bg, and *V*cg by

The inverter line-to-neutral voltages VaN, VbN, and VcN maybe expressed as

It is useful to recognize that the inverter voltages at terminals a, b, and c with respect to the midpoint (o) are given by

Where *V*og is the voltage at midpoint (*o*) with respect to ground(*g*). *V*og routinely fluctuates among three different voltage values *V*dc, 2*V*dc, and 3*V*dc as follows: +8*V*dc/3, +7*V*dc/3, +6*V*dc/3, +5*V*dc/3, +4*V*dc/3, +2*V*dc/3, 0, -2*V*dc/3, -4*V*dc/3, -5*V*dc/3, -6*V*dc/3, -7*V*dc/3, and -8*V*dc/3.

It is worth noting that all simulated waveforms are obtained at  $t1=t2=\cdots=t24=0.02/24$  s.

$$= 2 , + + \leq 5

+ + = 6 (5)$$

$$+ + + \geq 7$$

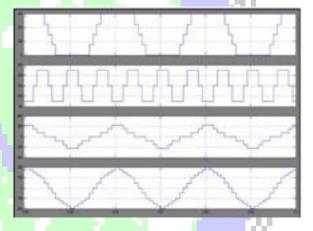

The simulated voltage waveforms of Vag, Vog ,Vao and VaN based on (1)–(5) are shown in Fig. 3 where, for instance, 13sequent voltage steps are seen in VaN waveform as follows:

TABLE II

SWITCHING STATES SEQUENCE OF THE PROPOSED

| INVERTER WITHIN ONE CYCLE | |

| -· -·         | Peri    | ON -        | ON -          | ON -               | ON -        |       |                |     |

|---------------|---------|-------------|---------------|--------------------|-------------|-------|----------------|-----|

|               | od      | swit        | swit          | swit               | switc       |       |                |     |

|               | T[s]    | ches        | ches          | ches               | hes         |       |                |     |

|               |         | Leg         | Leg           | Leg                | Casca       |       |                |     |

|               |         | a           | b             | c                  | ded         |       |                |     |

|               |         |             |               |                    | half-       |       |                |     |

| _: _:         | _ :     | _:          | _ :           | _ :                | bridge      |       | _:             |     |

| 400           | t1      | Q1          | Q4            | Q6                 | T1,         | 4     | 0              | 0   |

| - 410 -       | t2 - :  | Q1 - :      | S3, - :       | Q6-                | T4          | 4     | - :            | 0   |

| 410           | 12      | ŲI          | S3,<br>S4     | Qu                 | T1, T4      | 4 -   |                | U   |

| - 420 -       | t3 -    | Q1 - :      | S3, -         | Q6-                | T2, -       | 4 -   | 2 - :          | 0   |

| .20           |         | ν.          | S4            | 40                 | T3          |       | _              | Ü   |

| - 430 -       | t4 – :  | Q1 – :      | S3, - ·       | Q6-                | T1,         | 4     | 3 -            | 0   |

|               |         |             | S4            |                    | T3          |       |                |     |

| _ : 440 _ :   | t5 _ :  | Q1_:        | Q3 _ :        | Q6_                | T1, _ 1     | 4 _ : | 4 _ :          | 0   |

| 340           | t6      | S1,S        | Q3 ·          | Q6                 | T3<br>T1,   | 3 .   | 4 .            | 0   |

| - · · · · - · |         | 2 -         | Z             | <b>~</b> °_        | T3          |       |                |     |

| 240           | t7 ·    | S1,S -      | Q3 ·          | Q6                 | T2,         | 2 .   | 4 .            | 0   |

|               |         | 2 -         |               | _                  | T3 -        |       |                |     |

| . 140 .       | t8 .    | S1,S        | Q3 .          | Q6                 | T1,         |       | 4 .            | 0   |

| 040           | t9 - ·  | 2 - ;<br>Q2 | Q3            | Q6                 | T4 - T1,    | 0     | 4              | 0   |

| . 040         |         | Q2          | Q3 .          | Q0                 | T4 _        | · ·   | _ <del>-</del> | U   |

| 041           | t10     | Q2          | Q3            | S <mark>5</mark> , | T1,         | 0     | 4              | 0   |

| _: _:         | _ :     | _ :         | _ :           | S6_                | T4 _ :      | _ :   | _ :            |     |

| 042           | t11     | Q2          | Q3            | S5,                | T2,         | 0     | 4              |     |

| - 1 043 - 1   | .12 - : | 02-1        | 02 - :        | S6_                | T3          |       | :              | 2   |

| 043           | t12     | Q2          | Q3            | S5,<br>S6          | T1,<br>T3   | 0     | 4              | 2   |

| - · 044 - ·   | t13 -   | Q2 - '      | Q3 - ·        | Q5 <sup>-</sup>    | T1,         | 0     | 4              | 3   |

|               |         | ,           |               |                    | T3 .        |       |                |     |

| - · 034 - ·   | t14 - · | Q2 - ·      | S3, -         | Q5- ·              | T1, - ·     | 0 -   | 3              | 4   |

|               |         |             | S4            |                    | T3          |       |                | الب |

| - · 024 - ·   | t15 - · | Q2 - ·      | S3, -         | Q5-                | T2, -       | 0 -   | 2 - ·          | 4   |

| - : 014 - :   | 116     | 02          | S4 .          | 05                 | T3          |       |                | 4   |

| - 1014 - 1    | t16 - · | Q2 - ·      | S3, - ·<br>S4 | Q5-                | T1, -       | 0     |                | 4   |

| - 004 -       | t17     | Q2 - :      | Q4            | Q5-                | T1,         | 0 -   | 0 - :          | 4   |

| 001           | ,       | Q2          | ζ.            | 25                 | T4          | Ü     |                | ட்  |

| - 104 -       | t18     | S1,S-       | Q4 -          | Q5-                | T1, -       | _ :   | 0              | 4   |

|               |         | 2 .         |               |                    | T4          |       |                |     |

| - 204         | t19 - : | S1,S-       | Q4 -          | Q5-                | T2, -       | 2     | 0 - :          | 4   |

|               |         | 2           |               | 0.5                | T3          |       | 0              |     |

| _ 304         | t20     | S1,S_ :     | Q4            | Q5_                | T1,<br>T3   | 3 _   | 0              | 4   |

| 404           | t21     | Q1_:        | Q4_:          | Q5_                |             | 4 .   | 0 .            | 4   |

|               |         | Ψ¹          | ۷'            | Z-                 | T3          |       | ·              | •   |

| 403           | t22     | Q1 ·        | Q4 ·          | S5,                | T1,         | 4 ·   | 0 .            | 3   |

|               |         |             |               | S6-                | T3 -        |       |                |     |

| - : 402 _ :   | t23     | Q1_:        | Q4 _ :        | S5,                | T2,         | 4 .   | 0 _ :          | 2   |

| 401           | t24     | Ο1          | 04            | 56<br>S5           | 13<br>T1    | 4     | 0 .            |     |

| 401           |         | Z1 .        | ~ ·           | S5,<br>S6-         | T1,<br>T4 - |       |                |     |

|               |         |             |               |                    |             |       |                |     |

| _: _:         | _ :     | _ :         | _ :           | _ :                |             |       | _ :            |     |

|               |         |             |               |                    |             |       |                |     |

|               |         |             |               |                    |             |       |                |     |

In order to plot the space vector diagram of the proposed inverter in a stationary d-q reference frame, the following equations can be used to derive d and q voltage components for all inverter vectors:

$$= \frac{1}{(1-\epsilon)^{2}} (2 - \epsilon - \epsilon)$$

(6)

$$= \frac{1}{\sqrt{(1-\epsilon)^{2}}} (1 - \epsilon)$$

(7)

$$V = -\epsilon$$

(8)

For all switching states presented in Table II, Fig. 4 shows the space vector diagram for the proposed topology.

Fig.2.Switching states vectors of the proposed inverter in d-q reference frame.

# **SWITCHING ALGORITHM**

The staircase modulation can be simply implemented for the proposed inverter. Staircase modulation with selective harmonics the most common modulation technique used to control the fundamental output voltage as well as to eliminate the undesirable harmonic components from the output waveforms. An iterative method such as the Newton-Raphson method is normally used to find the solutions to (*N*-1) nonlinear transcendental equations. The difficult calculations and the need of high performance controller for the real application are the main disadvantages of such method.

Where wt is the electrical angle. Or

fundamental voltage without causing over modulation. As a result,  $M_a$  can reach to 1.15 and Sa, Sb, and Sc can be simply determined by integrating the reference line-to-ground voltages as

Comparison of the proposed modulation method with the staircase modulation with the selective harmonic method shows that the proposed modulation features less time and needs simple calculations. The inverter's operating switching states *Sal*, *Sb*, and *Sca*nd corresponding switching gate signals based on the proposed modulation method are shown in Fig. 5. It is clear TABLE III SWITCHING STATE Sal AND INVERTER LINE-TO-GROUND VOLTAGE

that the switching gate signals are generated within 24 different modes starting from (044) to (034). Since the proposed inverter has been designed to achieve nine voltage levels, the modulation index must be within range  $0.9 \le M_a \le 1.15$ . For modulation index  $M_a < 0.9$ , only two dc voltage supplies  $4V_{dc}$  and  $2V_{dc}$  are utilized and the behaviour of the proposed inverter becomes similar to the three-level multilevel inverter. Using (9)–(11) and substituting N = 3, the inverter's operating switching states Sa, Sb, and Scat  $M_a < 0.9$  can be defined. The operation principle of the proposed inverter at  $M_a < 0.9$  is illustrated in Table III. Fig. 6(a) and (b) shows the inverter line-to-line voltage waveforms at nine different modulation indices including the over modulation operation  $M_a = 0.8, 0.9, 1.05, 1.15$ , and 1.3.

# IV. EXTENDED STRUCTURE

It is noticeable that there is possibility to reach an output voltage with higher number of steps in the proposed multilevel inverter by extending the CHB circuit. Such extending can be done by adding more half-bridge cells connected in series as shown in Fig. 7(a) and (b). In order to achieve the desired number of voltage levels, three methods can be followed to determine the magnitudes of utilized dc voltage supplies.

1) All cells have an equal dc supply in magnitude.

$$= (1) = (1 + 1) = (13)$$

Where n is the number of utilized cells. The maximum number of voltage steps is related to the number of utilized cells by

$$N = n + 2 \tag{14}$$

The number of operation modes that makes the switching states sequence achieves the required output voltage waveform

$$M=6(N-1)$$

(15)

2) The magnitude of dc voltage supply used in each and every cell in a particular inverter is obtained as follows:

$$= (16)$$

$$= 2 (17)$$

$$= (18)$$

$$= (-1) = 1 + \frac{(-1)}{(19)}$$

$$N = 2 + \frac{(-1)}{(20)} (20)$$

$$M = 6(N-1) (21)$$

3) By making a binary (power of 2) relationship between thedc supplies of the CHB structure as follows:

$$= 2^{(\ )}(\ ) (22)$$

$$= 2^{(\ )}(\ ) (23)$$

Fig.3. Circuit diagram of the proposed three-phase N-level multilevel inverter

$$= 2( )( ) (24)$$

$$= (-1) = 1 + 2 = (2) (25)$$

$$N=1+2$$

(26)

M=6(N 1) (27)

Table IV illustrates some characteristics of the proposed methods.

TABLE IV

COMPARISON OF THE MAXIMUM NUMBER OF

VOLTAGE LEVELSWITH THE REQUIRED VALUE

OF DC VOLTAGE SUPPLIES AMONGTHE

PROPOSED METHODS

|    | Numb           |    | 1 <sup>st</sup> | Method                 |    | 2 <sup>n</sup> | d Met     | hod |           | 3 <sup>rd</sup> N | <b>M</b> etl         | od |  |

|----|----------------|----|-----------------|------------------------|----|----------------|-----------|-----|-----------|-------------------|----------------------|----|--|

| i  | er of<br>cells | i  | I               | i                      | i  | I              | I         |     | 1         |                   |                      |    |  |

| _1 | n<br>2         | -1 | N<br>4          | M<br>1 3               | -1 | 5 -1           | M 24 -1   | 4   | N         | - M               | 1<br>4 <sup>-1</sup> | 4  |  |

| _1 | 3              | -1 | 5 -1            | 8 2 -1 4               | _1 | 8 -1           | 42-1      | 7   | -1 9      | -1 4              | 8-1                  | 8  |  |

| _+ | 4              |    |                 | 4<br>3 <sup>-1</sup> 5 |    | 2              |           |     | 7         |                   |                      |    |  |

| _1 | 5              | -1 | 7 -1            | 0<br>3 - 1 6<br>6      | -1 | 1 - 1<br>7     | 96-1      | 16  | -1 3<br>3 | -1 1!<br>2        | 9-1                  | 32 |  |

|    | 6              | ٠. | 8               | 4 - · 7<br>2           |    | 2 -·<br>3      | 13_·<br>2 | 22  | - 6<br>5  | - · 3             | 8                    | 64 |  |

- \_\_\_\_ Based on the comparison carried among the proposed methods, the following are some observations.

1) Comparing to the second and third methods, the first method has a high modularity degree since the symmetric structure of CHB makes use of equal dc voltage supplies. This method helps the proposed inverter to reach all maximum number of voltage levels (4, 5, 6, 7, 8,...,N).

- 2) Since the second and third methods use the asymmetrical structure of CHB, the proposed inverter can reach the required output voltage and the maximum number of voltage levels such as 5, 8, 9, 12, 17,...with less number of dc voltage supplies and power electronic components.

#### **COMPARISON STUDY**

In order to investigate the capability of the suggested configuration, the proposed inverter is compared with different types of multilevel inverters such as NPC, FC, and CHB. It is evident that the suggested three-phase N-level multilevel inverter can considerably minimize the required number of power components. For the same number of output voltage levels ( $N \ge 4$ ), Table V explains the required number of dc voltage supplies, switches, clamping diodes, control signals, and balancing capacitors of the proposed N-level inverter compared with three existing inverters NPC, FC, and CHB. As shown in Fig. 8, it can be noticed that nearly more than two-thirds of number of switches can be counted out as N increases. For instance, at the same

number of voltage levels N = 17, and compared with the existing multilevel inverters which require 96 switches, the required number of switches for the proposed inverter is less since it requires 42 switches based on the first method, 22switches based on the second method, and 20 switches based on the third method. On the other hand, it is well known that the voltage and current ratings of the power components have an effect on the cost and realization of the multilevel inverter. Assuming that all power components have an equal current rating which is the rated current of the load (IL), the voltage ratings of these components depend on the magnitude of dc voltage supplies, voltage stress, and structure of the inverter. Considering that all inverters have the same input dc link which equals  $(N-1)V_{dc}$ , Table VI illustrates the rating requirements for the proposed inverter comparing with the rating requirements fort he existing inverters. It is observed that the inverter employs switching devices with high voltage rating. That results in high cost perswitch. Since the topology is introduced with reduced number of switches, gate driver circuit, diodes and no clamping capacitors are involved, the semiconductor devices expenses are considerably recovered.

# III. POWER CONVERSION EFFICIENCY AND TOTAL HARMONICDISTORTION (THD%)

In order to determine the efficiency of the proposed inverter, it is necessary to determine the value of conduction and switching power losses generated by the semiconductor components. Basically, the main losses in semiconductor components such as IGBTs and diodes are categorized into two groups: conduction loss  $(P_{con})$  and switching loss  $(P_{sw})$  as follows:

$$= \cdot \int () + \cdot \int () () (28)$$

$$= \cdot \int () (29)$$

Where  $E_{\rm on}(t)$  is a turn-on loss and  $E_{\rm off}(t)$  is a turn-off loss. Switching losses  $E_{\rm on}(t)$  and  $E_{\rm off}(t)$  are experienced during the ON and OFF states, respectively. While  $E_{\rm ff}(t)$  is the reverse recovery loss of the diode, the majority of switching loss, which is experienced when the diode is turned OFF (OFF state)

$$= \cdot \int_0$$

(30)

$$= \cdot \int_0$$

(31)

Conduction power losses of IGBT and diode are approximated based on their forward voltage drops  $V_{\rm on}$  IGBT ,  $V_{\rm on}$  diode, and the instantaneous current i(t) flowing

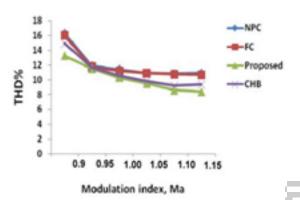

Fig. 5. NPC, FC, CHB, and proposed inverter: line-to-line voltage THD% versus *Ma*.

Moreover, the proposed inverter has been tested under different modulation indices ( $M_a = 0.9$ , 1, and 1.15). THD% of theoutput voltage can be calculated by

THD%=

$$\frac{\sum^{\infty}}{\times 100\%}$$

(41) where  $V_1$  and  $V_k$  are the fundamental component and harmonic order, respectively. NPC, FC, and—CHB

multilevel inverters have been tested under the same operating conditions. The goal of this test is to compare the proposed inverter with the existing inverters in term of THD%. Fig. 10 depicts THD% of the line to line voltage for all inverters within specific range of modulation indices [0.9–1.15]. It can be seen that the THD% of all inverter is slightly different. The measured values of THD% for the proposed inverter are within a range of 8.4–13.25%. As a result, the proposed inverter essentially adds the attractive aspects of the traditional two-level inverter such as less power components, simple working principle, and minimum conduction power loss to the main advantages of the multilevel inverter such as low THD% and high output voltage quality.

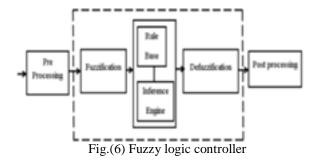

#### IV. FUZZY LOGIC CONTROLLER

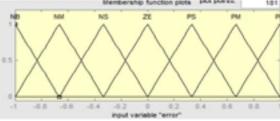

In FLC, basic control action is determined by a set of linguistic rules. These rules are determined by the system. Since the numerical variables are converted into linguistic variables, mathematical modeling of the system is not required in FC. The FLC comprises of three parts: fuzzification, interference engine and defuzzification. The FC is characterized as i. seven fuzzy sets for each input and output. ii. Triangular membership functions for simplicity. iii. Fuzzification using continuous universe of discourse. iv. Implication using Mamdani's, 'min' operator. v. Defuzzification using the height method.

**Fuzzification:** Membership function values are assigned to the linguistic variables, using seven fuzzy subsets: NB (Negative Big), NM (Negative Medium), NS (Negative Small), ZE (Zero), PS (Positive Small), PM (Positive Medium), and PB (Positive Big). The partition of fuzzy subsets and the shape of membership CE(k) E(k) function adapt the shape up to appropriate system. The value of input error and change in error are normalized by an input scaling factor

|         | 1   |                | ' Tal        | ole I F      | uzzy R           | ules         |            |    |

|---------|-----|----------------|--------------|--------------|------------------|--------------|------------|----|

| Change  | e ˈ |                |              | :            | Error            |              |            |    |

| in erro | r ' | $N\bar{B}$     | NM           | NS           | $\mathbf{Z}^{-}$ | PS           | . PM       | PB |

| NB      |     | $P\bar{B}$     | PB           | PB           | PM               | PM           | PS         | Z  |

| NM      |     | ΡB             | PB           | ŀ PM̄        | PM               | PS           | <u>'</u> Z | Z  |

| NS      |     | PB             | PM           | PS           | PS               | $\mathbf{Z}$ | NM         | NB |

| Z       |     | PB             | PM           | PS           | Z                | NS           | NM         | NB |

| PS      |     | PM             | PS           | $\mathbf{Z}$ | NS               | NM           | NB         | NB |

| PM      |     | PS             | $\mathbf{z}$ | NS           | NM               | NM           | NB         | NB |

| PB      |     | $\overline{Z}$ | NS           | NM           | NM               | NB           | NB         | NB |

|         |     |                |              |              |                  |              |            |    |

In this system the input scaling factor has been designed such that input values are between -1 and +1. The triangular shape of the membership function of this arrangement presumes that for any particular E(k) input there is only one dominant fuzzy subset. The input error for the FLC is given as

$$E(k) = \frac{(\ )}{(\ )} \frac{(\ )}{(\ )}$$

(14)

$$CE(k) = E(k) - E(k-1)$$

(15)

Fig.(7) Membership functions

**Inference Method:** Several composition methods such as Max–Min and Max-Dot have been proposed in the literature. In this paper Min method is used. The output membership function of each rule is given by the

minimum operator and maximum operator. Table 1 shows rule base of the FLC.

**Defuzzification:** As a plant usually requires a non-fuzzy value of control, a defuzzification stage is needed. To compute the output of the FLC, "height" method is used and the FLC output modifies the control output. Further, the output of FLC controls the switch in the inverter. In UPQC, the active power, reactive power, terminal voltage of the line and capacitor voltage are required to be maintained. In order to control these parameters, they are sensed and compared with the reference values. To achieve this, the membership functions of FC are: error, change in error and output.

The set of FC rules are derived from  $u=-[\alpha E + (1-\alpha)*C]$

Where  $\alpha$  is self-adjustable factor which can regulate the whole operation. E is the error of the system, C is the change in error and u is the control variable. A large value of error E indicates that given system is not in the balanced state. If the system is unbalanced, the controller should enlarge its control variables to balance the system as early as possible. set of FC rules is made using Fig.(7) is given in Table 1.

# V. MATLAB CIRCUIT MODEL

MATLAB/Simulink model of the proposed inverter shown in Fig. 1 has been developed to study the conduction and switching power losses. The proposed inverter is designed to deliver output power of  $P_{\text{out}} = 1.9$  kW. To simplify the losses calculation, a curve-fitting tool of MATLAB is used to approximate these curves by exponential equations [35].

Fig.8. MATLAB Circuit diagram of the proposed threephase 9-level multilevel inverter

#### VI. SIMULATION RESULTS

Fig.9. Simulated waveforms of Vab, Vbc, and Vca with corresponding switching gate signals for the proposed inverter at fundamental frequency f = 50 Hz.

Fig. 10. Simulated waveforms of Vag, Vog, Vao and VaNfor the proposed inverter f = 50 Hz.

Fig. 11. Inverter's operating switching states *Sa*, *Sb*, and *Sc* with corresponding witching gate signals based on the proposed modulation method.

Fig.12. Simulated waveforms of Vab at different modulation indices for the proposed inverter: (a) Ma = 0.9, 1.05, and 1.15 and (b) Ma = 0.8 and 1.3

# VII. CONCLUSION

A new topology of the three-phase nine-level multilevel by using fuzzy logic controller. The proposed topology results in reduction of installation area and cost. The fundamental frequency staircase modulation technique was comfortably employed and showed high flexibility and simplicity in control. Moreover, the proposed configuration was extended to N-level with different methods. Inverter was introduced. The suggested configuration was obtained from reduced number of power electronic components. The obtained simulation and hardware results met the desired output. Hence, subsequent work in the future may include an extension to higher level with other suggested methods. For purpose of minimizing THD%, a selective harmonic elimination pulse width modulation technique can be also implemented.

# REFERENCES

- [1] J. Rodriguez *et al.*, "Multilevel inverters: A survey of topologies, controls, and applications," *IEEE Trans. Ind. Electron.*, vol. 49, no. 4, pp. 724–738, Aug. 2002.

- [2] L. G. Franquelo*et al.*, "The age of multilevel converters arrives," *IEEEInd. Electron. Mag.*, vol. 2, no. 2, pp. 28–39, Jun. 2008.

- [3] I. Colak*et al.*, "Review of multilevel voltage source inverter topologies and control schemes," *Energy Convers. Manage.*,vol. 52, pp. 1114–1128,2011.

- [4] J. Rodriguez *et al.*, "Multilevel converters: An enabling technology for high-power applications," *Proc. IEEE*, vol. 97, no. 11, pp. 1786–1817, Nov. 2009.

- [5] J. Rodriguez *et al.*, "A survey on neutral-point-clamped inverters," *IEEETrans. Ind. Electron.*, vol. 57, no. 7, pp. 2219–2230, Jul. 2010.

- [6] S. Gui-Jia, "Multilevel DC-link inverter," *IEEE Trans. Ind. Appl.*, vol. 41, no. 3, pp. 848–854, May/Jun. 2005.

- [7] P. Fang Zheng, "A generalized multilevel inverter topology with self voltage balancing," *IEEE Trans. Ind. Appl.*, vol. 37, no. 2, pp. 611–618, Mar./Apr. 2001. [8] J. A. Ferreira, "The multilevel modular DC converter," *IEEE Trans. PowerElectron.*, vol. 28, no. 10, pp. 4460–4465, Oct. 2013.

- [9] K. Ilves*et al.*, "A new modulation method for the modular multilevel converter allowing fundamental switching frequency," *IEEE Trans. PowerElectron.*, vol. 27, no. 8, pp. 3482–3494, Aug. 2012.

- [10] W. Yong and W. Fei, "Novel three-phase three-level-stacked neutral point clamped grid-tied solar inverter with a split phase controller," *IEEE Trans.Power Electron.*, vol. 28, no. 6, pp. 2856–2866, Jun. 2013.